数据锁存器(Data Latch)

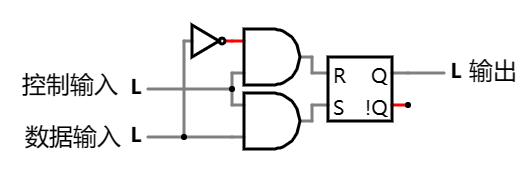

在先前, 为解决 R 和 S 两个输入必须反向的问题, 我们引入了一个反相器; 为进一步解决锁存器按需存储的问题, 我们又引入了传输门结构:

至此, 整体在结构上已经能够满足我们对锁存的要求了.

仔细观察次结构, 有两个输入端: 一个是数据输入, 一个是控制输入; 有一个输出端 Q, 即所存储的值.

在满足 R 和 S 总是反向的前提下, !Q 和 Q 总是一正一反, !Q 可以说是冗余的, 这个输出是不需要的.

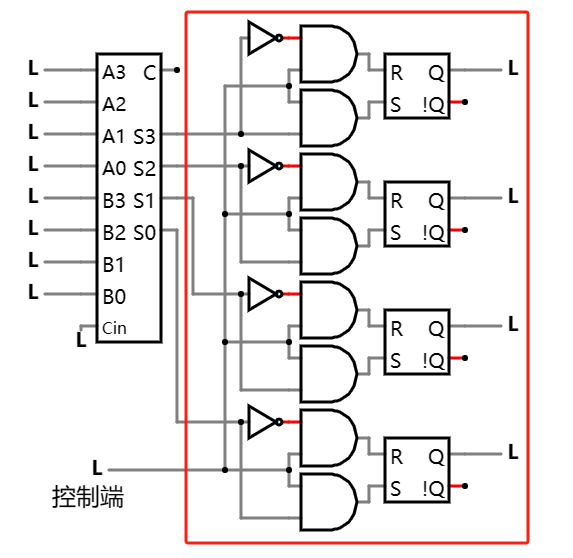

显然, 这个结构还是具有一定的复杂性, 特别是为了存储四位加法器的输出, 使用了整整四套这样的结构, 显得非常庞大:

可以看到它比加法器还大!

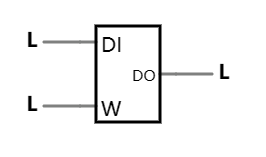

因此, 有必要进行一定的封装, 将细节隐藏起来, 这样封装起来的结果就是所谓的 数据锁存器(Data Latch):

注: DI 代表数据输入(Data Input);

W 代表控制输入. W 即为 Write, 意为写入控制, 当它是高电平时, 即表示允许将数据输入的值写入到缓存中.

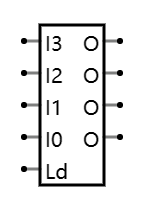

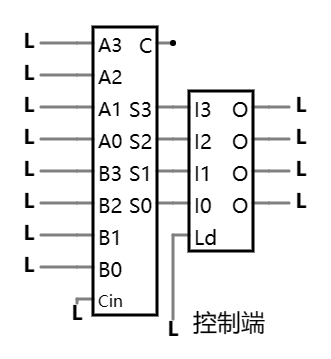

将多个一位的数据锁存器整合一起来, 即可以构成一个多位的数据锁存器, 如下是一个四位的锁存器:

注: 此处使用了系统自带的多位锁存器(可通过 "菜单--绘制--数字芯片--添加锁存器" 添加).

其中 Ld 即是控制输入, Ld 即为 load, 表示装载, 也即写入的意思;

I0~I3 为四位数据输入(Input);

四个 O 表示四位输出(Output), 处于上面的为高位;

另: 初始默认为四位, 可以调整为更多位, 但不能调为更少, 至少四位.

有了此四位锁存器模块后, 对四位加法器的和的锁存就简单很多了:

四位锁存器用于锁存四位加法器的和 在线可互动操作示例

操作与之前类似, Ld 端先设置为低电平, 即不进行锁存.

在加法器输入端置入要加的数, 并等加法器输出的和稳定后, 将锁存器的控制端 Ld 置为高电平, 结果就会被锁存.

之后, 如需置入新的加数做进一步的加法, 只需再度将 Ld 端设为低电平.

等新的加数设好, 并等和的输出稳定后, 又可再度将 Ld 置为高电平锁存新的结果.

注: 严格地讲, 系统自带的这个锁存器的 Ld 控制端并非是电平触发, 而是更高级的边缘触发的.

我们将在后面再分析这两种触发方式的区别, 目前而言, 边缘触发的模式在上述操作情形下与电平触发并无效果上的区别.

至此, 数据锁存的问题已经解决, 结构也已经简化, 可以做多次的累加.

但累加的过程仍然比较繁琐:

- 需要手动将锁存结果再转设在加法器输入端, 如果数据位特别多, 则非常麻烦, 也很容易出错.

- 需要特别注意操作锁存控制端的正确顺序, 才能确保结果被正确锁存.

这些问题我们将在后续章节加以探讨并解决.