锁存器增加输入控制

我们现在遇到了新的问题, 为解决锁存器无法复位的问题, 引入了反相器的结构, 但又同时导致了无法缓存的问题.

这也是电路设计中经常碰到的一个场景, 而它的解决方案也很简单, 或者说不简单, 那就是引入更复杂的结构.

这么做是有道理的, 因为场景变得更复杂, 所以对应的解决方案也应该相应变得更复杂. 因为从本质上讲, 解决方案是对复杂现实世界的一个抽象映射.

以简单对简单, 以复杂对复杂, 这很自然, 也很公平.

尽管这看上去有点像"水多了加面, 面多了又加水"...

仔细分析了目前所遇到的问题, 严格来说, 真正的问题并不是锁存器无法缓存, 而是它无时无刻都在缓存!

因为它直连了加法器的输出, 之间没有任何的隔离, 这就导致了无论是需要还是不需要的时候, 它都在缓存.

所以解决方案也就呼之欲出了, 就是增加隔离, 增加控制, 使得只在我们需要的时候, 才进行缓存.

还记得之前曾经引入过的 传输门 吗?

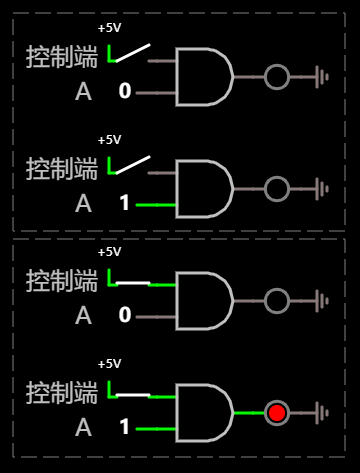

它有一个信号端和一个控制端, 通过一个与门来实现. 当控制端处于低电平时, 根据与门的真值表特性, 无论另一个信号端是什么电平, 输出总是低电平.

换言之, 信号端的高电平无法传输到输出端, 如此一来就实现了控制传输的目的.

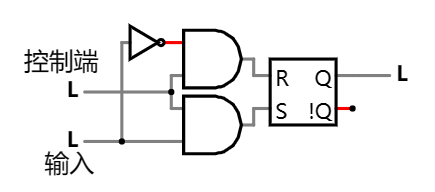

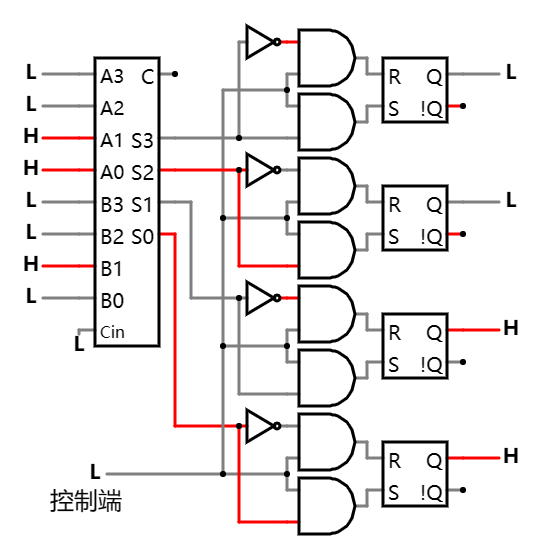

而这里, 为解决类似的问题, 也引入两个传输门结构以及一个相应的控制端:

这里让 R 和 S 的输入端都先经过传输门, 而当传输门的控制信号为低电平时, 传输门关闭, 两个传输门的输出总是低电平.

而根据真值表的特性, 当 R 和 S 都是低电平时, 它将保持之前缓存的结果.

而当需要更新缓存结果时, 则需要把传输门的控制端置为高电平, 此时传输门打开, 锁存器缓存新的结果

而当结果被缓存后, 只需再把传输门的控制端置为低电平, 传输门再次关闭. 之后, 可以撤掉加法器的两个输入 A 和 B, 而之前的加和继续缓存在锁存器中.

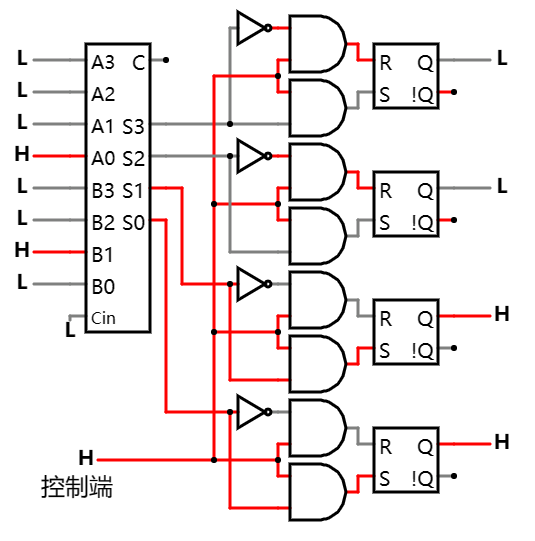

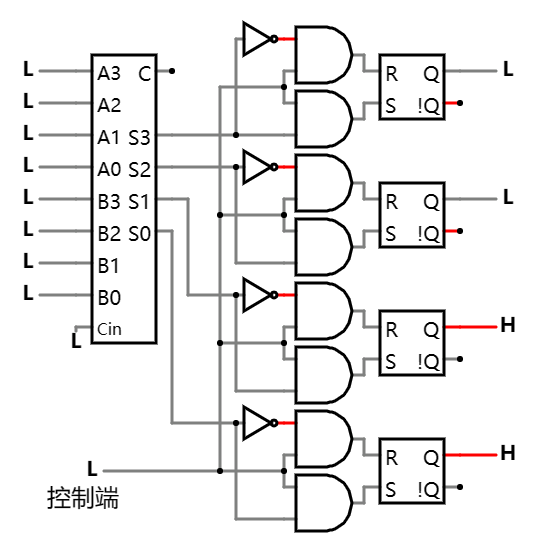

问题解决了! 而回到最初希望的连续做加法 1+2+3 的问题上, 先做 1+2, 然后把结果 3 缓存.

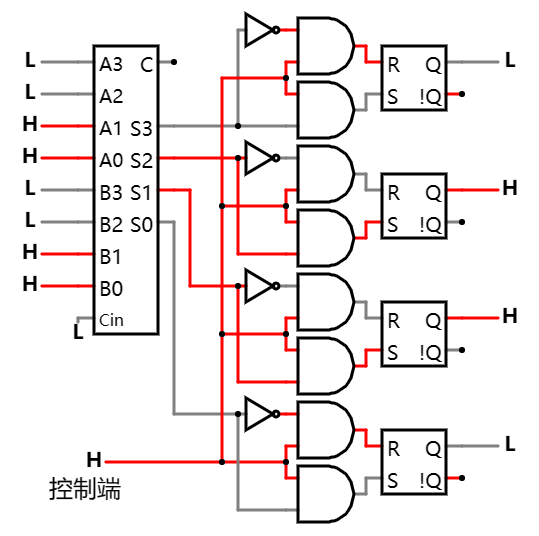

当传输门关闭后, 我们可以从容的对照着锁存器的输出, 然后再把这个结果设回加法器的输入端 A 中:

请注意, 因为加法器的输出总是实时的, 而此刻另一个输入 B 仍然是 2, 所以一个暂时的结果 3+2=5(0101) 出现在加法器的输出端.

不过无需担心, 因为传输门被关闭了, 之前锁存的结果不会变化, 仍然是3(0011).

当再把 B 端设为第三个加数 3 后, 加法器输出 3+3 的结果, 也即最终的 1+2+3 的结果 6(0110), 此时只需再度打开传输门, 新的结果又会被缓存.

再度打开传输门并缓存最终的结果 在线可互动操作示例

反复操作, 就可以加起更多的数的和, 从而实现多个数的累加!

自然不方便的地方还是有的, 就是需要手动的把锁存器的结果再次置入加法器的 A 端, 这很繁琐, 而且很容易出错.

能否让结果自己回到输入端呢? 在下一章节, 我们再探讨这个问题.